芬蘭坦佩雷--(美國商業資訊)--由芬蘭SoC Hub聯盟開發的首款單晶片系統(SoC)已經流片。專案合作夥伴接下來將專注於改進SoC的設計、自動化和效能。該聯盟將開發三款晶片,第一款將於2022年初做好部署準備。專案有助於增強歐洲的技術主權。

此新聞稿包含多媒體內容。完整新聞稿可在以下網址查閱:https://www.businesswire.com/news/home/20211213005527/en/

芬蘭SoC Hub已著手將SoC設計領域發展成為歐洲的先鋒,並提高芬蘭的競爭地位。去年,芬蘭坦佩雷大學(Tampere University)和諾基亞(Nokia)共同發起了SoC Hub倡議。合作夥伴推展的共同創造活動遠遠超出了傳統研究專案的範圍。

坦佩雷大學SoC設計副教授Ari Kulmala表示:「開發這款SoC的方法與工業生產所使用的方法相同,例如可測試性設計、廣泛的驗證以及關注系統級整合而非單一模組。」

Kulmala指出,該晶片隨附一個開發套件,能夠整合到各種其他系統中,因此還可以由外部利害關係人進行測試。

SoC Hub專案的主要目標之一是實現新構思的快速原型開發,例如,在物聯網(IoT)、機器學習和矽中的5G及6G技術。

新流片的Ballast晶片是三款晶片系列中的第一款。該晶片將由全球首屈一指的半導體晶片製造商台積電(TSMC)製造。

該晶片採用台積電新近開發的22奈米超低漏電(Ultra Low Leakage)製程製造,特別適合物聯網和邊緣設備。Ballast包含若干不同的RISC-V CPU內核、一個數位訊號處理器、一個人工智慧加速器、豐富的類似感測器的介面和一個連接FPGA的擴充介面。另外,晶片還實作了一個包括驅動程式、軟體開發工具和晶片除錯支援在內的完整軟體堆疊。該晶片同時支援即時作業系統和Linux。

imec(一家奈米與數位技術研發中心)旗下的imec.IC-link業務開發總監Bas Dorren表示:「我們很高興能與SoC Hub團隊合作。他們開發晶片的速度非常快,工作品質也堪稱一流。」

未來兩年內還有兩款晶片流片

雖然晶片尺寸較大,但卻在短時間內製作完成。歸功於良好的團隊精神和相關專家的專長和經驗,這個宏大的目標最終得以實現。

坦佩雷大學資訊工程學系主任Timo Hämäläinen表示:「為了實現大學與企業合作夥伴之間的順暢協作,我們做了大量工作。一些早期職業研究人員參與了Ballast的設計,因此有機會將他們從研究中獲得的知識應用到工業專案中。」

除了SoC的開發之外,專案的第一階段也是一項重大任務,它包括建立聯盟和準備必要的軟體和授權合約。該聯盟由坦佩雷大學和諾基亞領導,合作夥伴包括CoreHW、VLSI Solution、Siru Innovations、TTTEch Flexibilis、Procemex、Wapice和Cargotec。

在這個由芬蘭國家商務促進局(Business Finland)資助的專案中,三款SoC將在2023年底前流片。專案聯盟將對晶片使用案例進行規劃。

Timo Hämäläinen強調:「在專案的下一個階段,我們將能夠更多地關注SoC的系統、自動化和效能。儘管已經實現了我們的第一個目標,但我們將立刻繼續推動專案。投資SoC開發的時機是現在,而不是未來。」

關於坦佩雷大學

坦佩雷大學是一座多學科綜合性大學,也是芬蘭規模第二大的大學。我們的研究和學習由三大方向引領:技術、健康和社會。該大學致力於解決人類社會面臨的各項重大挑戰並創造新的機會。其研究幾乎涵蓋了所有國際認可的領域。坦佩雷大學和坦佩雷應用科學大學共同組成了坦佩雷大學社區,擁有超過3萬名學生和近5,000名教職員工。www.tuni.fi/en

原文版本可在businesswire.com上查閱: https://www.businesswire.com/news/home/20211213005527/en/

免責聲明:本公告之原文版本乃官方授權版本。譯文僅供方便瞭解之用,煩請參照原文,原文版本乃唯一具法律效力之版本。

聯絡方式:

Timo Hämäläinen

坦佩雷大學資訊工程學系主任

timo.hamalainen@tuni.fi

Ari Kulmala

坦佩雷大學單晶片系統設計副教授

ari.kulmala@tuni.fi

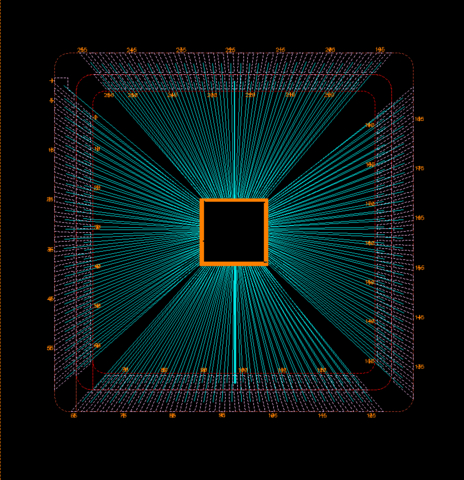

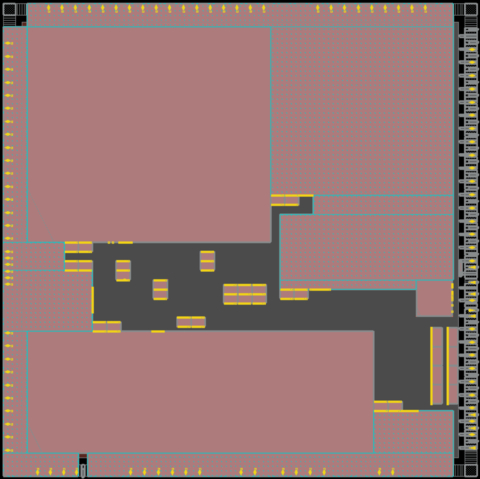

接合圖圖像顯示晶片IO Pad如何連接到封裝引腳。封裝被焊接到印刷電路板上。佈局圖顯示功能塊在晶片上的實際位置。側面顯示與封裝引腳相連的IO Pad。照片:SoC Hub。(圖片:美國商業資訊)

SoC Hub的營運以坦佩雷大學和企業之間的創新合作為基礎。專案小組成員在坦佩雷大學合影。照片:Jonne Renvall/坦佩雷大學(照片:美國商業資訊)

接合圖圖像顯示晶片IO Pad如何連接到封裝引腳。封裝被焊接到印刷電路板上。佈局圖顯示功能塊在晶片上的實際位置。側面顯示與封裝引腳相連的IO Pad。照片:SoC Hub。(圖片:美國商業資訊)