東京--(美國商業資訊)--記憶體解決方案全球領導者東芝記憶體株式會社(Toshiba Memory Corporation)今日宣布成功開發出一種可實現高速、高容量固態硬碟的橋接晶片。東芝利用所開發的佔用面積小、低功耗的橋接晶片,成功透過比無橋接晶片的傳統方法更少的高速訊號線連接更多的快閃記憶體晶片。公司於2月20日在舊金山2019國際固態電路會議(ISSCC 2019)上宣布了這一成果。

此新聞稿包含多媒體內容。完整新聞稿可在以下網址查閱:https://www.businesswire.com/news/home/20190221005378/en/

在固態硬碟中,多個快閃記憶體晶片與管理其執行的控制器相連。一旦與控制器介面相連的快閃記憶體晶片數量增加,其操作速度降低,因此限制了可連接的晶片的數量。為了提高容量,則需要增加介面數量,但這會造成需將大量的高速訊號線連接到控制器上,因此增加了實現在固態硬碟板上進行佈線的難度。

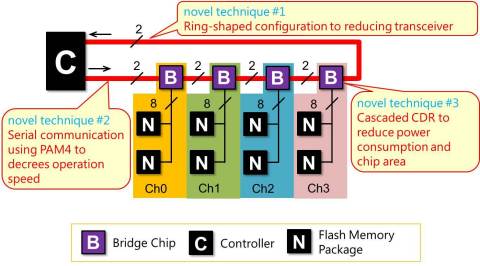

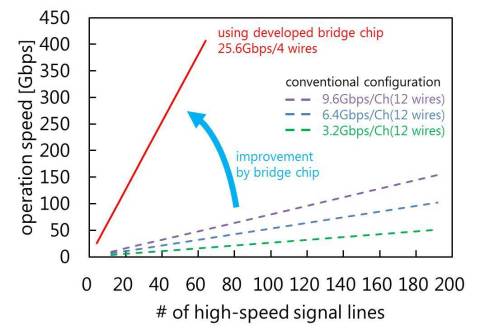

東芝利用所開發的可連接控制器與快閃記憶體晶片(圖1)的橋接晶片解決了這一難題,並成功實現了三項創新技術:菊輪鍊連接技術*1,以環形方式連接控制器和多個橋接晶片;使用PAM 4*2進行序列通訊;以及抖動*3改進技術,可無需在橋接晶片中使用PLL電路*4。採用這些技術,能夠降低橋接晶片的開銷,並且僅透過幾條高速訊號線(圖2)便能高速執行大量的快閃記憶體晶片。

橋接晶片和控制器的環形結構將橋接晶片所需的收發器數量從兩對減少到一對,縮小了橋接晶片的面積。此外,在控制器與菊輪鍊式橋接晶片之間採用PAM 4序列通訊,可降低橋接晶片電路的執行速度,緩解它們所需承受的性能壓力。新CDR*5利用PAM 4的特點改進抖動性,因此無需在橋接晶片中使用PLL電路,同時有助於縮小晶片面積、降低功耗。

橋接晶片原型採用28nm CMOS製程製造,按照環形菊輪鍊形式將四個橋接晶片與控制器連接對其性能進行了評估。該評估證實了所有橋接晶片和控制器在25.6 Gbps的速度下均能實現良好的PAM 4通訊性能,而且也能夠實現BER*6低於10-12。

接下來,東芝會進一步提升橋接晶片性能、縮小晶片面積和降低功耗,繼續致力於開發工作,以實現前所未見的高速、大型存放區能力。

註

*1 菊輪鍊:一種將多個晶片依序連接在一起的連接方式

*2 PAM 4:4電平脈脈波振幅調變(包含4數值資料)

*3 抖動:時鐘或訊號波形時域的波動

*4 PLL:鎖相環路(生成精確基準訊號的電路)

*5 CDR:時脈資料回復(從已接收的訊號中回復資料和時脈的電路)

*6 BER:位元錯誤率(值越低,性能越高)

關於東芝記憶體株式會社

作為記憶體解決方案全球領導者,東芝記憶體株式會社致力於快閃記憶體和SSD的開發、生產和銷售。2018年6月,東芝記憶體株式會社被一家由Bain Capital領銜的產業財團收購。東芝記憶體株式會社開創性地開發出了一系列尖端的記憶體解決方案和服務,豐富了人們的生活並擴大了社會的視野。該公司創新的3D快閃記憶體技術BiCS FLASH™將對先進智慧手機、PC、SSD、汽車和資料中心等高密度應用領域記憶體的未來產生深遠影響。有關東芝記憶體株式會社的更多詳情,請造訪:https://business.toshiba-memory.com/en-apac/top.html

原文版本可在businesswire.com上查閱:https://www.businesswire.com/news/home/20190221005378/en/

免責聲明:本公告之原文版本乃官方授權版本。譯文僅供方便瞭解之用,煩請參照原文,原文版本乃唯一具法律效力之版本。

聯絡方式:

東芝記憶體株式會社

Kota Yamaji

商業規劃部

電話:+81-3-6478-2319

semicon-NR-mailbox@ml.toshiba.co.jp

圖1 使用橋接晶片連接(圖片:美國商業資訊)

圖2 橋接晶片帶來的改進(圖片:美國商業資訊)